## A NOVEL FAULT TOLERANT ARCHITECTURE ON A RUNTIME RECONFIGURABLE FPGA

## A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

ΒY

İBRAHİM AYDIN COŞKUNER

# IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONICS ENGINEERING

NOVEMBER 2006

Approval of the Graduate School of Natural and Applied Sciences

Prof. Dr. Canan ÖZGEN Director

I certify that this thesis satisfies all the requirements as a thesis for the degree of Master of Science.

Prof. Dr. İsmet ERKMEN Head of Department

This is to certify that we have read this thesis and that in our opinion it is fully adequate, in scope and quality, as a thesis for the degree of Master of Science.

Prof. Dr. Hasan Cengiz GÜRAN Supervisor

Examining Committee Members

| Assist. Prof. Dr. Cüneyt BAZLAMA | ÇCI (METU, EE)   |  |

|----------------------------------|------------------|--|

| Prof. Dr. Hasan Cengiz GÜRAN     | (METU, EE)       |  |

| Assist. Prof. Dr. İlkay ULUSOY   | (METU, EE)       |  |

| Dr. Şenan Ece SCHMIDT            | (METU, EE)       |  |

| M.Sc. Alper ÜNVER                | (TÜBİTAK – SAGE) |  |

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

İbrahim Aydın COŞKUNER

## ABSTRACT

# A NOVEL FAULT TOLERANT ARCHITECTURE ON A RUNTIME RECONFIGURABLE FPGA

COŞKUNER, İbrahim Aydın M.S., Department of Electrical and Electronics Engineering Supervisor: Prof. Dr. Hasan Cengiz Güran

November 2006, 128 Pages

Due to their programmable nature, Field Programmable Gate Arrays (FPGAs) offer a good test environment for reconfigurable systems. FPGAs can be reconfigured during the operation with changing demands. This feature, known as Runtime Reconfiguration (RTR), can be used to speed-up computations and reduce system cost. Moreover, it can be used in a wide range of applications such as adaptable hardware, fault tolerant architectures.

This thesis is mostly concentrated on the runtime reconfigurable architectures. Critical properties of runtime reconfigurable architectures are examined. As a case study, a Triple Modular Redundant (TMR) system has been implemented on a runtime reconfigurable FPGA. The runtime reconfigurable structure increases the system reliability against faults. Especially, the weakness of SRAM based FPGAs against Single Event Upsets (SEUs) is eliminated by the designed system. Besides, the system can replace faulty elements with non-faulty elements during the operation. These features of the developed architecture provide extra safety to the system also prolong the life of the FPGA device without interrupting the whole system.

**Keywords:** Runtime Reconfiguration, Partial Reconfiguration, Fault Tolerant Reconfigurable Systems

# ÇALIŞIRKEN YENİDEN BİÇİMLENDİRİLEBİLİR FPGA ÜZERİNDE HATAYA DAYANIMLI YENİ BİR YAPI

COŞKUNER, İbrahim Aydın Yüksek Lisans., Elektrik ve Elektronik Mühendisliği Bölümü Tez Yöneticisi: Prof. Dr. Hasan Cengiz Güran

#### Kasım 2006, 128 Sayfa

Alan Programlanabilir Kapı Dizinleri (FPGA) programlanabilir yapıları sayesinde, yeniden biçimlendirilebilir sistemler için uygun bir yapı sunarlar. FPGA gelen değişik ihtiyaçlara göre çalışma esnasında yeniden biçimlendirilebilir. Çalışırken Yeniden Biçimlendirme (RTR) olarak bilinen bu özellik sayesinde işlemler daha hızlı yapılabilir ve toplam sistem maliyeti düşürülebilir. Ayrıca RTR uyarlanabilir donanımlar ve hataya dayanımlı yapılar gibi birçok alanda kullanılabilir.

Bu tez çalışırken biçimlendirilebilir yapılar üzerine yoğunlaşmıştır. Çalışırken biçimlendirilebilir yapıların önemli özellikleri incelenmiştir. Örnek olarak Üçlü Modüler Yedekleme (TMR) sistemi, çalışırken biçimlendirilebilir bir yapı üzerinde uygulanmıştır. Çalışırken yeniden biçimlendirilebilir yapı sistemin hatalara karşı güvenilirliğini artırmıştır. Özellikle FPGA'lerin Tekli Hata Oluşumlarına (SEU) karşı olan zaafları tasarlanan sistem sayesinde giderilmiştir. Ayrıca sistem hatalı elemanları hatasız olanlarla çalışma sırasında değiştirebilmektedir. Geliştirilen mimarinin bu özellikleri sayesinde sistem daha güvenilir olmuş ve FPGA'in kullanım ömrü sistem durdurulmadan uzatılabilir hale gelmiştir.

Anahtar Kelimeler: Çalışırken Yeniden Biçimlendirme, Kısmi Yeniden Biçimlendirme, Hataya Dayanıklı Yeniden Biçimlendirilebilir Sistemler

To My Family

# ACKNOWLEGMENTS

I would like to thank my supervisor Professor Hasan Güran, for his guidance and advices throughout the preparation of this thesis. Thanks to his advices and helpful criticisms, this thesis is completed.

I also thank to my family for their great encouragement, for their great support, and for their endless love.

I am very grateful to Türkmen Canlı, for the boards he brought at a critical time. I am also grateful to Salih Zengin for his ideas, suggestions, and technical support.

Special thanks goes to Yüksel Subaşı for the moral support he has given to me when I was near to give up, I also thank to Yiğiter Yüksel for his guidance and my colleagues for their help and friendship during this period. I also greatly appreciate Ahmet Coşar for the PCB he produced.

TÜBİTAK-SAGE who supported this work is greatly acknowledged.

# **TABLE OF CONTENTS**

| ABST                | RACT   | iv                                                          |  |  |

|---------------------|--------|-------------------------------------------------------------|--|--|

| ÖZ                  |        | V                                                           |  |  |

| ACKN                | OWLE   | GMENTSvii                                                   |  |  |

| TABLI               | E OF C | ONTENTSviii                                                 |  |  |

| LIST C              | OF TAI | BLESxii                                                     |  |  |

| LIST OF FIGURESxiii |        |                                                             |  |  |

| LIST C              | OF AB  | BREVATIONSxvi                                               |  |  |

| СНАР                | TERS   |                                                             |  |  |

| 1 INTF              | RODUC  | CTION1                                                      |  |  |

| 1                   | .1     | Overview1                                                   |  |  |

| 1                   | .2     | Objective of the Thesis2                                    |  |  |

| 1                   | .3     | Tools Used                                                  |  |  |

| 1                   | .4     | Organization of the Thesis4                                 |  |  |

| 2 BAC               | KGRC   | UND5                                                        |  |  |

| 2                   | 2.1    | Reconfigurable Computing5                                   |  |  |

|                     | 2.1.   | 1 The Aim of Reconfigurable Architectures                   |  |  |

| 2                   | 2.2    | Granularity of Reconfigurable Architectures6                |  |  |

| 2                   | 2.3    | Reconfiguration Approaches12                                |  |  |

| 2                   | 2.4    | Reconfiguration Time16                                      |  |  |

| 2                   | 2.5    | Partially Runtime Reconfigurable FPGAs17                    |  |  |

|                     | 2.5.   | 1 Reconfiguration Times of FPGAs19                          |  |  |

| 2                   | 2.6    | Application Areas of Reconfigurable Architectures19         |  |  |

|                     | 2.6.   | 1 Easy Prototyping – Low Volume Products19                  |  |  |

|                     | 2.6.   | 2 In-Field Upgrades20                                       |  |  |

| 2                   | 2.7    | Application Areas of Runtime Reconfigurable Architectures20 |  |  |

|                     | 2.7.   | 1 Cost and Power Reduction21                                |  |  |

|      | 2.     | 7.2    | Adaptable Computing                                     | 22     |

|------|--------|--------|---------------------------------------------------------|--------|

|      | 2.     | 7.3    | Speeding-up Computations                                | 23     |

|      | 2.     | 7.4    | Fault Tolerant Systems                                  | 24     |

|      | 2.8    | Applic | cation in this Work                                     | 24     |

| 3 XI | LINX F | PGA A  | RCHITECTURE AND TOOLS                                   | 25     |

|      | 3.1    | Main   | Structure of Xilinx FPGAs                               | 25     |

|      | 3.     | 1.1    | Configurable Logic Block Structure                      | 26     |

|      | 3.     | 1.2    | Input Output Block Structure                            | 26     |

|      | 3.     | 1.3    | Routing Structure                                       | 27     |

|      | 3.2    | Config | guration Architecture of Xilinx FPGAs                   | 29     |

|      | 3.     | 2.1    | Column and Difference Based Reconfiguration             | 30     |

|      | 3.     | 2.2    | Glitchless Reconfiguration                              | 31     |

|      | 3.     | 2.3    | Clocking Logic                                          | 31     |

|      | 3.     | 2.4    | Suitable Configuration Options for Runtime Reconfigurat | ion 31 |

|      | 3.3    | Conve  | entional Design Flow for Xilinx FPGAs                   | 36     |

|      | 3.4    | Tools  | for Partial Reconfiguration of Xilinx FPGAs             | 38     |

|      | 3.     | 4.1    | XAPP290                                                 | 38     |

|      | 3.     | 4.2    | JBITS                                                   | 39     |

| 4 M  | ODULE  | BASE   | D PARTIAL RECONFIGURATION                               | 41     |

|      | 4.1    | Colun  | nn Based Reconfiguration                                | 42     |

|      | 4.     | 1.1    | Restrictions of Partial Reconfigurable Design           | 43     |

|      | 4.     | 1.2    | Bus Macros                                              | 43     |

|      | 4.     | 1.3    | Clocking Logic                                          | 44     |

|      | 4.2    | Imple  | mented Simple Partial Reconfigurable Architecture       | 45     |

|      | 4.3    | Xilinx | Tools and Implementation                                | 46     |

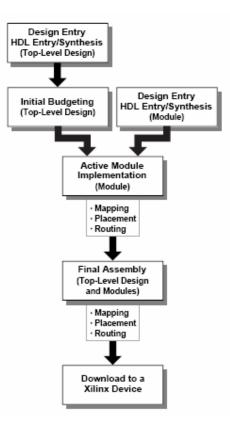

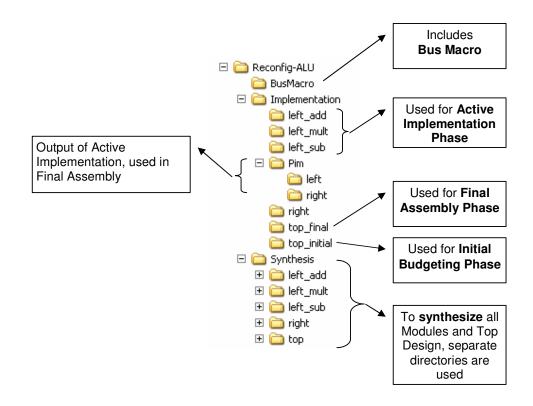

|      | 4.     | 3.1    | Modular Design Flow Overview                            | 46     |

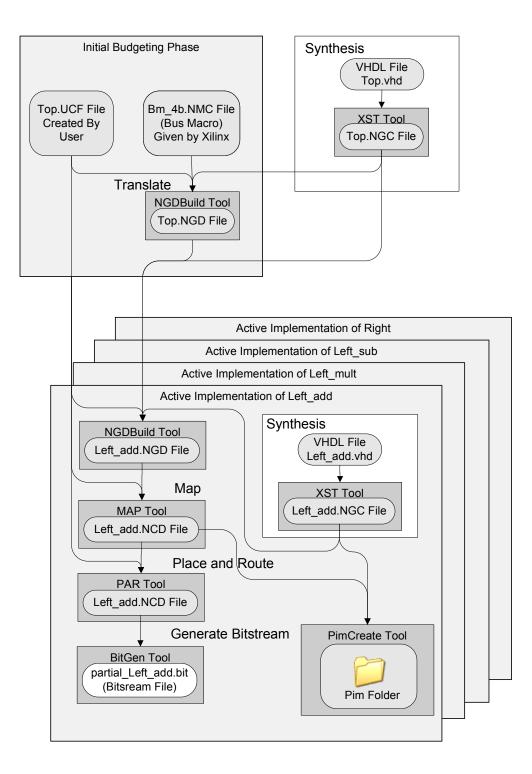

|      | 4.     | 3.2    | Module Entry and Synthesis                              | 50     |

|      | 4.     | 3.3    | Implementation                                          | 51     |

|      |        | 4.3.3. | .1 Initial Budgeting Phase                              | 53     |

|      |        | 4.3.3. | 2 Active Module Implementation Phase                    | 58     |

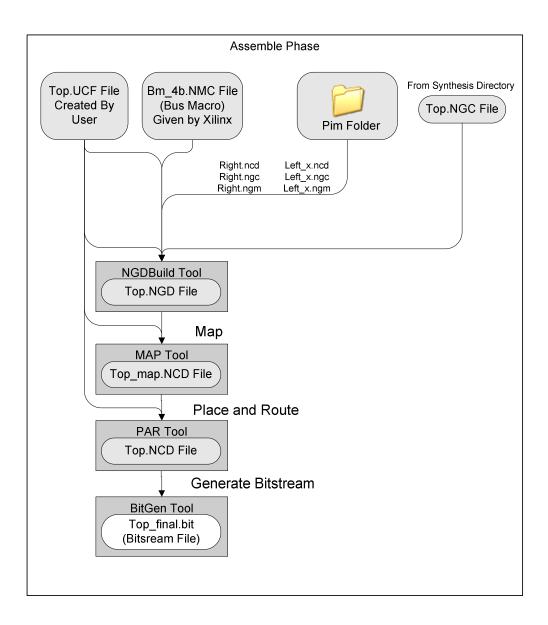

|      |        | 4.3.3. | 3 Final Assembly Phase                                  | 59     |

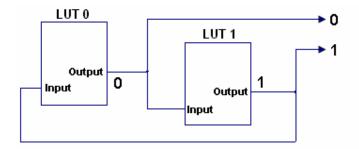

|      | 4.     | 3.4    | Creating "Logic 0" and "Logic 1"s                       | 63     |

|      | 4.4    | Enoo   | untered Problems and Solutions                          | 64     |

| 4         | .4.1    | Bus  | Macro Error and Its Solution          | .65 |

|-----------|---------|------|---------------------------------------|-----|

| 4         | .4.2    | Sec  | cond Bus Macro Error and Its Solution | .66 |

| 5 A TMR S | SYSTEM  | ON   | A RUNTIME RECONFIGURABLE ARCHITECTURE | .68 |

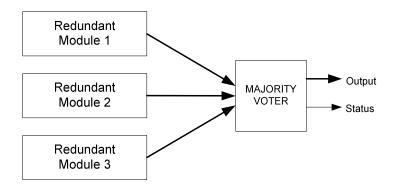

| 5.1       | Backg   | rour | nd                                    | .68 |

| 5         | 5.1.1   | Fau  | Ilt Tolerance                         | .69 |

|           | 5.1.1.1 | 1    | Redundancy                            | .69 |

|           | 5.1.1.2 | 2    | Availability                          | .69 |

| 5         | 5.1.2   | Trip | ble Modular Redundancy (TMR)          | .69 |

| 5         | 5.1.3   | Rol  | Iback and Roll-forward                | .70 |

| 5         | 5.1.4   | Fau  | ılt Types                             | .71 |

|           | 5.1.4.  | 1    | Transient Faults                      | .71 |

|           | 5.1.4.2 | 2    | Permanent Faults                      | .72 |

| 5.2       | Relate  | ed W | /ork                                  | .73 |

| 5.3       | Desigr  | ned  | Architecture                          | .76 |

| 5         | 5.3.1   | Ge   | neral Overview of the System          | .76 |

|           | 5.3.1.1 | 1    | Addressed Error Types                 | .77 |

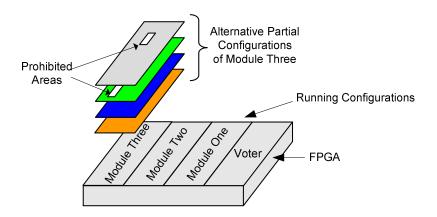

|           | 5.3.1.2 | 2    | Partial Runtime Reconfigurable Design | .77 |

| 5         | 5.3.2   | Hai  | dware Used in the Design              | .78 |

|           | 5.3.2.  | 1    | Digilent D2-SB System Board           | .79 |

|           | 5.3.2.2 | 2    | Digilent DIO Board                    | .80 |

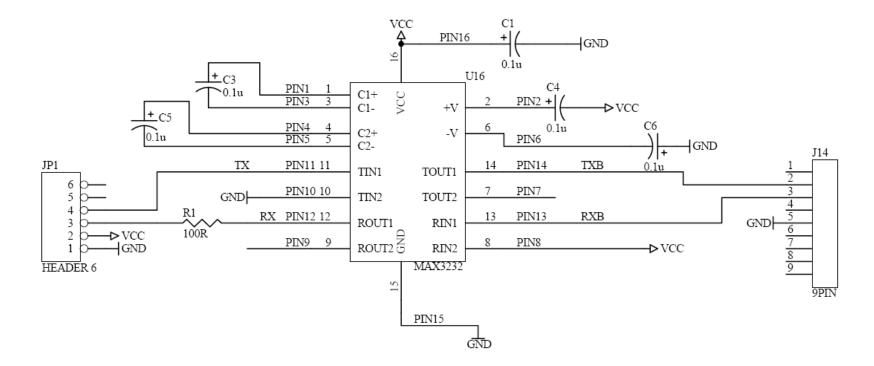

|           | 5.3.2.3 | 3    | RS232 to LVTTL Converter Board        | .80 |

|           | 5.3.2.4 | 4    | Parallel Cable III                    | .81 |

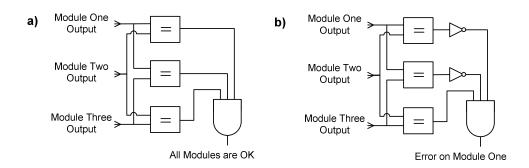

| 5         | 5.3.3   | Wo   | rking Principle of the TMR            | .81 |

| 5         | 5.3.4   | VH   | DL Design of the TMR Circuit          | .82 |

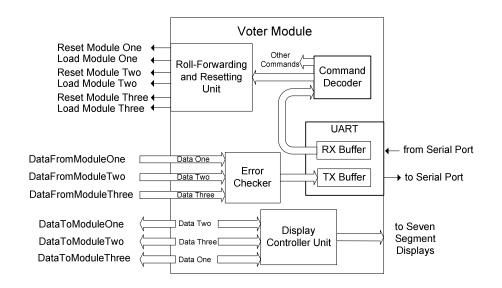

|           | 5.3.4.1 | 1    | Voter Module                          | .83 |

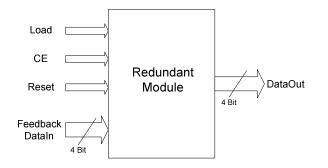

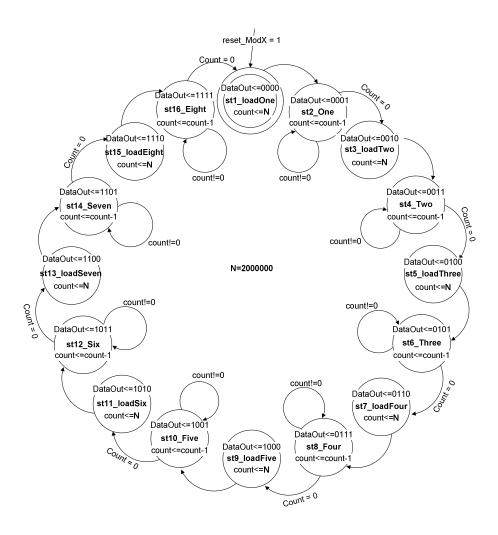

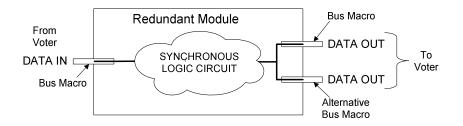

|           | 5.3.4.2 | 2    | A Redundant Module                    | .87 |

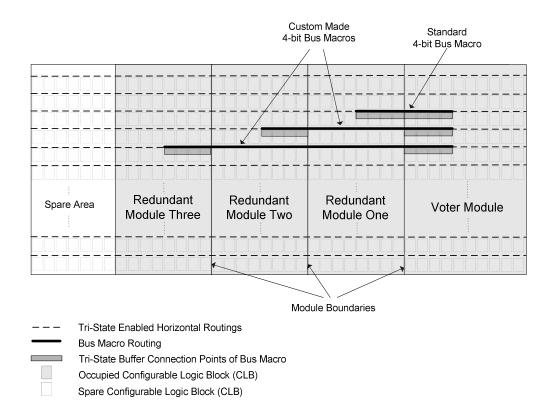

| 5         | 5.3.5   | Par  | tial Reconfigurable FPGA Design       | .90 |

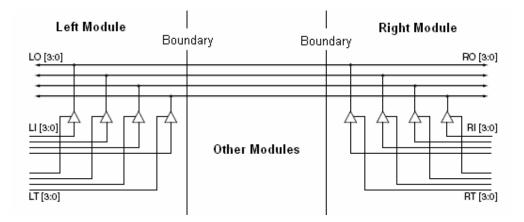

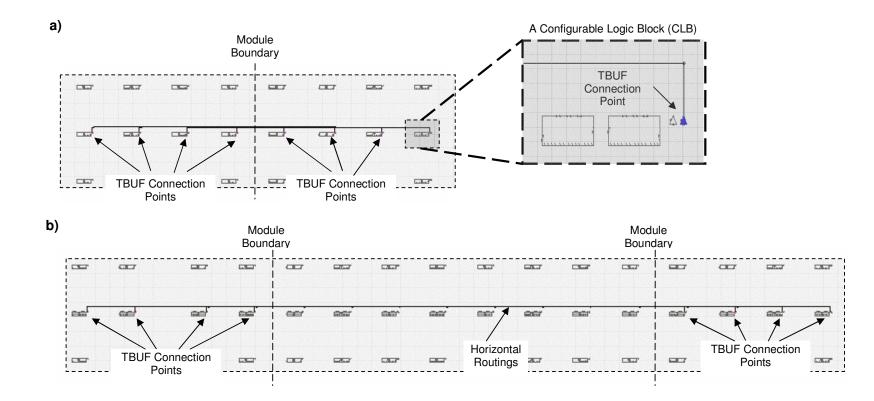

|           | 5.3.5.1 | 1    | Modified Bus Macro                    | .92 |

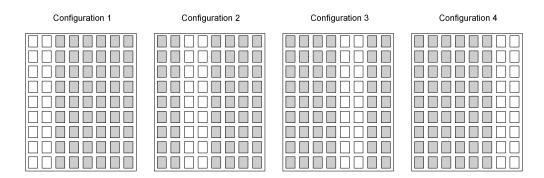

|           | 5.3.5.2 | 2    | Partial Configurations                | .95 |

|           | 5.3.5.3 | 3    | Batch Files for Modular Design Flow   | .96 |

| 5         | 5.3.6   | Elir | ninating Faults                       | .97 |

|           | 5.3.6.  | 1    | Eliminating Single Event Upsets       | .97 |

|           | 5.3.6.2 | 2    | Eliminating Permanent Faults          | .98 |

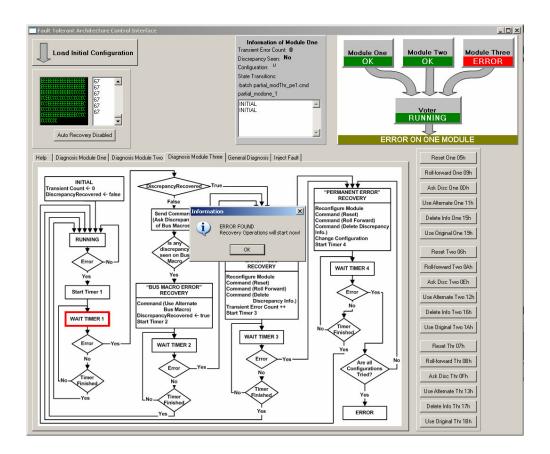

| 5         | 5.3.7   | PC   | Program                               | .99 |

|     |                                           | 5.3.7.1    | Communication with Serial Port                | 101 |

|-----|-------------------------------------------|------------|-----------------------------------------------|-----|

|     | 5.3.7.2                                   |            | Batch Files for Configuration                 |     |

|     | 5.3.7.3                                   |            | Running Batch Files from Borland C++ Buider   |     |

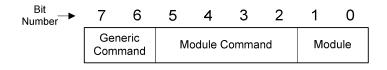

|     | 5.                                        | 3.8 I      | Protocol between PC Program and Voter Module  |     |

|     | 5.                                        | 3.9 I      | Fault Elimination Algorithm Running on the PC |     |

|     | 5.                                        | 3.10 I     | Fault Injection                               | 105 |

|     |                                           | 5.3.10.    | Bitstream Modification                        |     |

|     |                                           | 5.3.10.2   | 2 VHDL Code Modification                      | 110 |

| 6 C | CONCLU                                    | ISIONS     |                                               | 111 |

|     | 6.1                                       | Conclu     | sions Based on the Work                       | 111 |

|     | 6.2                                       | Recom      | mended Future Works                           | 113 |

| RE  | FEREN                                     | CES        |                                               | 114 |

| AP  | PENDIC                                    | ES         |                                               |     |

| Α   | PCB a                                     | nd Sche    | matics of the RS232 Circuit                   | 119 |

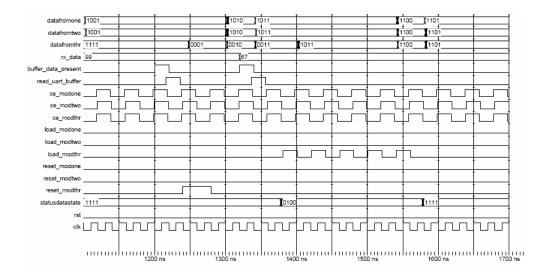

| В   | Simula                                    | ation of 1 | wo Roll Forwarding Methods                    | 121 |

| С   | User C                                    | Constrair  | t File of the TMR Design                      | 122 |

| D   | PACE                                      | and FPG    | A Editor View of the TMR Design               | 124 |

| Е   | Source Files of Designed Architectures126 |            |                                               | 126 |

# LIST OF TABLES

| Table 3-1: JTAG Pins and their descriptions                                                       | 35  |

|---------------------------------------------------------------------------------------------------|-----|

| Table 3-2: Standard Design Flow Operations and Tools of Xilinx FPGAs                              | 38  |

| Table 4-1: Descriptions of Files that are used for Module Based Partial           Reconfiguration | 49  |

| Table 4-2: Truth Tables of Dummy Look Up Tables                                                   | 63  |

| Table 5-1: Status Descriptions and their corresponding ASCII values                               | 84  |

| Table 5-2: Definitions and codes of Module Commands                                               | 85  |

| Table 5-3: Occupied Area of the Modules                                                           | 92  |

| Table 5-4: Different Bus Macro Functions and Their Sources                                        | 93  |

| Table 5-5: FPGA Editor Symbols and Their Functions                                                | 108 |

| Table 5-6: Truth Table of LUT Function Before and After a SEU Injection                           | 109 |

| Table E-1: The Directories and Files in the CDROM                                                 | 126 |

# LIST OF FIGURES

| Figure 2-1: Comparison of Microprocessors, ASICs, and Reconfigurable<br>Architectures                                                |

|--------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2-2: General Structure of a Fine-Grained Architecture7                                                                        |

| Figure 2-3: Basic Structure of a Fine-Grained Logic Cell on an FPGA8                                                                 |

| Figure 2-4: Reconfigurable Data Unit of KressArray [6]9                                                                              |

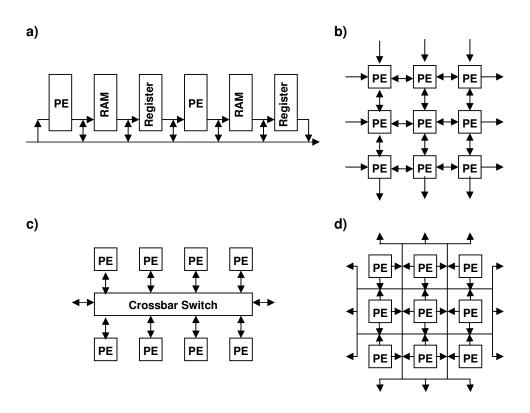

| Figure 2-5: Array Structures of Coarse Grain Architectures a) Linear Array b)<br>Mesh c) Crossbar d) 2-Dimensional Array10           |

| Figure 2-6: A Datapath Equation and Hardware Mapping [6] a) Equation mapped to the node levels b) Hardware mapping of the equation11 |

| Figure 2-7: Dynamic Reconfiguration of Hardware12                                                                                    |

| Figure 2-8: A Partially Reconfigurable Device and its Configurations                                                                 |

| Figure 2-9: Self-Reconfiguration from External Configuration Port15                                                                  |

| Figure 2-10: Self-Reconfiguration using Internal Configuration Port15                                                                |

| Figure 2-11: Required Reconfiguration Times for Different Application Types16                                                        |

| Figure 2-12: An Example of Hardware Operating System [13]17                                                                          |

| Figure 3-1: General Structure of Spartan 2E FPGAs [31]25                                                                             |

| Figure 3-2: A CLB of a Virtex-E (or Spartan 2E) device26                                                                             |

| Figure 3-3: Input/Output Block Structure of Virtex-E Device                                                                          |

| Figure 3-4: General Routing Matrix and its Connections [31]28                                                                        |

| Figure 3-5: Horizontal Longlines that traverse all along the FPGA28                                                                  |

| Figure 3-6: Configuration Columns and Frames of Xilinx XCV50 device                                                                  |

| Figure 3-7: SelectMAP Configuration Signals on Xilinx FPGA                                                                           |

| Figure 3-8: ICAP Configuration Signals on Xilinx FPGA                                                                                |

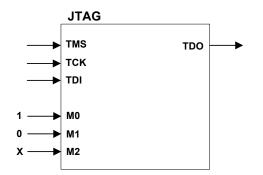

| Figure 3-9: JTAG Configuration Signals on Xilinx FPGA                                                                                |

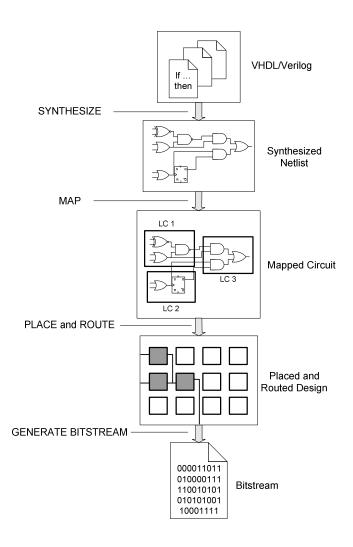

| Figure 3-10 Standard Design Flow for an FPGA Design37                                                                                |

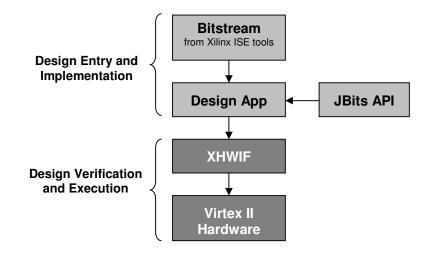

| Figure 3-11: Design Flow of Runtime Reconfiguration using JBits [39]39                                                               |

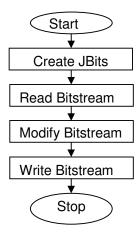

| Figure 3-12: JBits Application Flow40                                                                                                |

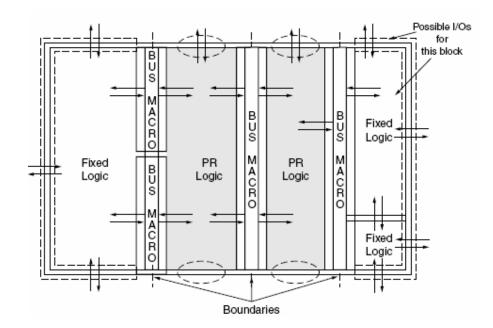

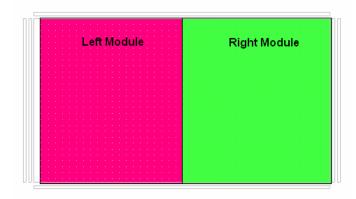

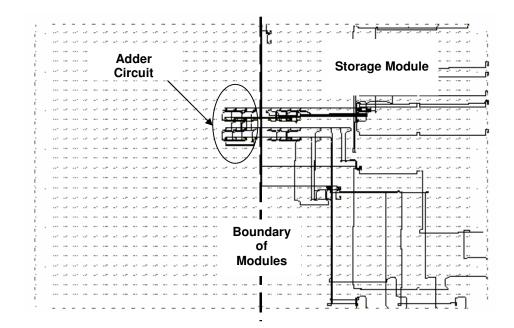

| Figure 4-1: Design Layout with Two Reconfigurable Modules [35]42                                                                     |

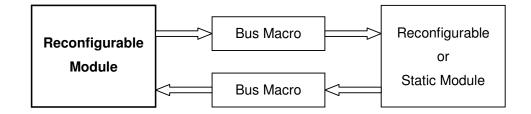

| Figure 4-2: Communication with Reconfigurable Modules43                                                                              |

| Figure 5-13: Modified Bus Macro that connects Two Non-Adjacent Modules93                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5-14: FPGA Editor Snapshots of Bus Macros a) Standard Bus Macro<br>connecting Two Adjacent Modules b) Modified Bus Macro connecting Two<br>Non-Adjacent Modules |

| Figure 5-15: Alternative Partial Configurations of Module Three95                                                                                                      |

| Figure 5-16: Connections of Bus Macros on a Redundant Module96                                                                                                         |

| Figure 5-17: Alternative Configurations of a Module                                                                                                                    |

| Figure 5-18: Screenshot of the Supervisor PC Program100                                                                                                                |

| Figure 5-19: An example of Communication Protocol Commands during Error<br>Recovery Operation of a Module103                                                           |

| Figure 5-20: Flowchart of Fault Recovery Algorithm that Runs on the PC Program                                                                                         |

| Figure 5-21: Configurable Logic Block in Editing Mode107                                                                                                               |

| Figure 5-22: A virtual faulty CLB and it is mapping on alternative placements110                                                                                       |

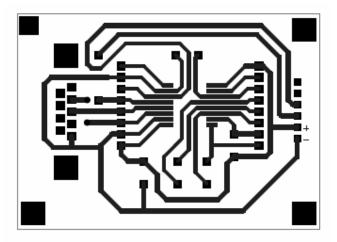

| Figure A-1: Top Layer PCB of RS232 Circuit119                                                                                                                          |

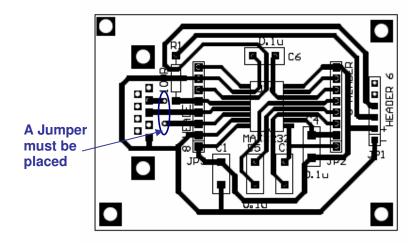

| Figure A-2: Top Overlay PCB of RS232 Circuit119                                                                                                                        |

| Figure A-3: Schematic of RS232 Circuit120                                                                                                                              |

| Figure B-1: Simulation of Roll Forwarding Method 1 (Constant Frequency Rate)<br>                                                                                       |

| Figure B-2: Simulation of Roll Forwarding Method 2 (Variable Frequency Rate)<br>                                                                                       |

| Figure D-1: Module Placements of the TMR Design (Snapshot is taken with PACE)                                                                                          |

| Figure D-2: FPGA Editor View of TMR Design125                                                                                                                          |

# LIST OF ABBREVATIONS

ALU Arithmetic Logic Unit API **Application Programming Interface** ASIC Application Specific Integrated Circuit CAD **Computer Aided Design** CRC Cyclic Redundancy Check DSP **Digital Signal Processing** FPGA Field Programmable Gate Array FSM **Finite State Machine** GUI Graphical User Interface HDL Hardware Description Language I/O Input-Output IP Intellectual Property LUT Look-up Table PCB Printed Circuit Board PE **Processing Element** PROM Programmable Read Only Memory RA **Reconfigurable Architecture** RAM Random Access Memory RTR **Runtime Reconfiguration** SDR Software Defined Radio SEU Single Event Upset SoC System on Chip TMR Triple Modular Redundancy UART Universal Asynchronous Receiver and Transmitter VHDL VHSIC Hardware Description Language VHSIC Very High Speed Integrated Circuit

## **CHAPTER I**

## INTRODUCTION

### 1.1 OVERVIEW

The microprocessors provide a flexible environment for the programmers. Any type of algorithm can be computed on a general-purpose microprocessor. However, this flexibility has a significant cost on computation time. The calculations are done on the same hardware resources for all type of applications (i.e. one instruction is handled at a time). Calculating algorithms in such serial structures results in performance degradation.

If the computations can be done in parallel, a significant speed-up can be achieved. *Reconfigurable architectures* provide enough hardware resources that can be used to make computations in parallel. Moreover, their flexible structure allows constructing different hardware configurations.

Reconfigurable architectures contain configurable connections and a plenty of logic resources. An application specific hardware can be formed by configuring these connections. These configurations can be stored by SRAM or Flash based switches. If SRAM based architecture is used on the reconfigurable device, infinite number of configurations can be loaded at different times. Loading a different configuration is called *reconfiguration*.

The most popular reconfigurable architecture is the Field Programmable Gate Array (FPGA). It is commercially available and used for high performance applications. FPGA is the ideal component for low volume products and it is used for prototyping Integrated Circuits (IC). With continuously increasing capacities and falling prices, they are also used in mass products now.

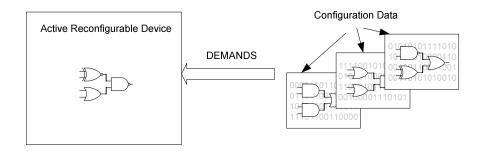

Normal usage of reconfigurable architectures such as FPGAs is as follows; all the demands is ready before the device runs. Then according to these

demands, only one final configuration is prepared and loaded to the reconfigurable device. Only this configuration runs on the device until a power-down occurs.

However, SRAM based reconfigurable devices enable changing configuration data whenever required. Some devices use this property to change configuration data during the device is running. Therefore, changing demands during the operation can be satisfied by reconfiguring these devices. This type of reconfiguration is called Runtime Reconfiguration (RTR). RTR introduced "Virtual Hardware" concept. It allows same hardware sources to be used for different purposes at different times by reconfiguring hardware. Therefore, a runtime reconfigurable architecture enables using unlimited circuits in only one chip by time multiplexing them.

RTR can be used in adaptable hardware applications, in-field upgrade of hardware. Other advantages of time multiplexing sources by RTR are reduced cost and reduced power of the system. Most importantly, speed-up can be obtained for different types of computations. Consequently, adding RTR property to the reconfigurable architectures offer new opportunities for digital systems.

### 1.2 OBJECTIVE OF THE THESIS

The main aim of the thesis is to investigate Runtime Reconfigurable architectures and to design one such architecture. In order to design a reconfigurable system, capabilities of a Field Programmable Gate Array (FPGA) are examined. Afterwards, a fault tolerant architecture is designed that use runtime reconfiguration to eliminate the faults. This design is implemented and tested on a runtime reconfigurable FPGA.

#### 1.3 TOOLS USED

In order to implement a runtime reconfigurable system, some hardware and software tools were used. The tools are the following:

#### **Hardware Tools**

• D2SB Board from Digilent Inc.

- Personal Computer (PC)

- DIO1 Board from Digilent Inc.

- Custom made RS232 to TTL Converter Card

- Xilinx Parallel Cable III

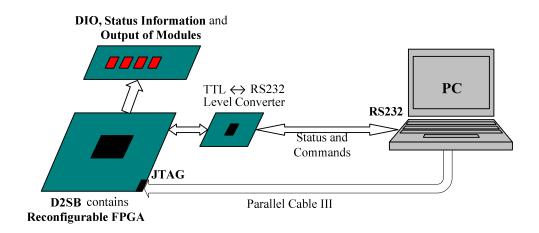

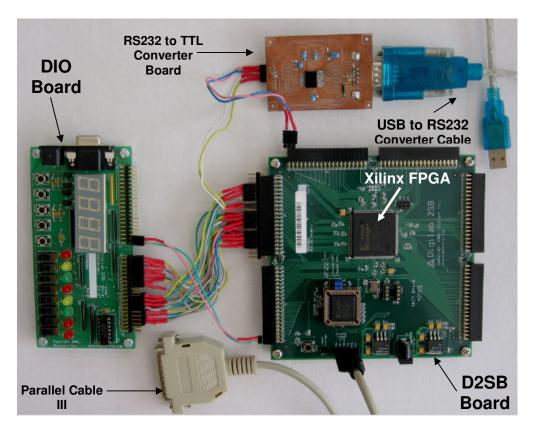

D2SB Board, which is at the heart of the reconfigurable system, contains a Xilinx Spartan 2 - 200E FPGA on it. Personal Computer (PC) is responsible for the reconfiguration processes of the FPGA. DIO1 Board is used to display real-time information. An RS232 to TTL converter board is used for the communication of PC and FPGA. The configuration data of the FPGA is downloaded from the PC using Xilinx Parallel Cable III. Detailed description of the hardware configuration will be given in Chapter 5.

#### **Software Tools**

- Xilinx ISE 6.3i SP2

- VHDL

- Borland C++ Builder 5

Xilinx ISE is a CAD tool that is necessary to generate FPGA designs for Xilinx FPGAs. It has a Graphical User Interface (GUI) that can be used for standard FPGA designs. However, the GUI is not enough to achieve a runtime reconfigurable design. The command line tools of ISE such as NgdBuild, MAP, PAR, and BitGen are used in this design.

VHDL is a language that can describe hardware. It is used to generate circuits on FPGA. Files written in VHDL are synthesized using Xilinx Synthesis Tool (XST).

Borland C++ Builder 5 is used to generate a visual PC program. This program communicates with FPGA board and manages reconfiguration processes. The program also provides a user interface that enables user manipulation and shows the status of the system.

## 1.4 ORGANIZATION OF THE THESIS

The thesis is composed of six chapters. The chapter contents are the following:

In Chapter 2, a literature survey is done on reconfigurable computing Basic terms and concepts of reconfigurable architectures are explained. The application areas of the reconfigurable architectures are also given. Alternative reconfigurable FPGAs from different vendors are discussed and their critical characteristics are compared.

In Chapter 3, Xilinx FPGA and its features that enable runtime reconfiguration are discussed. Some properties of Xilinx FPGAs are explained from this viewpoint.

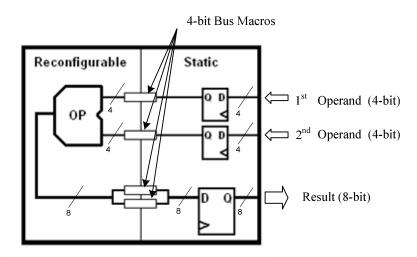

In Chapter 4, a simple reconfigurable application is mapped on Xilinx FPGA. The steps of designing a reconfigurable system are explained using that simple application. All tools and their batch files are described in detail.

In Chapter 5, a runtime reconfigurable TMR system that is designed to be highly fault tolerant is presented.

In Chapter 6, a conclusion of this thesis is given. Moreover, planned future works are given in this chapter.

## **CHAPTER II**

## BACKGROUND

In this chapter, basic concepts about reconfigurable architectures will be explained. In addition, some applications based on reconfigurable architectures will be emphasized.

## 2.1 RECONFIGURABLE COMPUTING

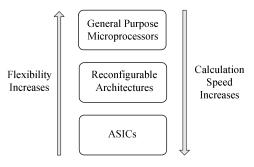

In the last few decades, *Reconfigurable Computing* has become popular in the area of computer architectures. Reconfigurable systems arise to compensate the differences of flexible microprocessors and high-speed ASIC circuits. A reconfigurable architecture takes advantages of both systems. It is more flexible than ASIC circuits since it can be reconfigured with changing computing needs. In addition, it has better performance than processors since it implements the desired algorithm on a dedicated hardware. As seen in Figure 2-1, reconfigurable architectures take place in between microprocessors and ASICs according to the flexibility and speed.

Figure 2-1: Comparison of Microprocessors, ASICs, and Reconfigurable Architectures

FPGAs are the first reconfigurable devices introduced as a commercial product. The first vendor Xilinx has produced FPGAs at mid-1980s with a very limited capacity. The capacity improvement of FPGAs has nearly followed Moore's Law [1]. Today FPGAs have millions of logical gates. Hence, it is possible to implement more than one medium-sized processor inside one FPGA. Xilinx MicroBlaze, Altera Nios are examples of such processors. The improvement of these reconfigurable devices leads to raise academic research on reconfigurable architectures.

#### 2.1.1 The Aim of Reconfigurable Architectures

The hardware on reconfigurable architectures can be reconfigured if the demands are changed. This flexibility allows reusability of the hardware resources. Therefore, reconfigurable architectures can be used for all applications that can benefit from hardware reusability. Some general benefits of this flexibility are speeding-up calculations and resource saving.

## 2.2 GRANULARITY OF RECONFIGURABLE ARCHITECTURES

Reconfigurable architectures generally composed of array of reconfigurable unit blocks and routing sources that connect these blocks. The size of these unit blocks reflects granularity of the architecture. The granularity of these devices ranges from fine to coarse grain. They can be mainly classified as

- Fine-Grained,

- Coarse-Grained and

- Heterogeneous Architectures.

Fine-grained architectures are suitable for bit-level manipulations and contain elements such as LUT. On the other side, coarse grain architectures have elements such as ALU or small processor, which makes them suitable for word level computations. Heterogeneous architectures also become available to use advantages of both architectures.

#### **Fine Grained Architectures**

*Fine-grained* architectures are intended to implement bit level logic circuits. Calculations that have arbitrary bit width can be done by using fine-grained architectures. The advantage of fine-grained architectures is that it can map any logical circuit on the hardware. However, the overhead of routing resources increases as a cost of this flexibility.

The well-known example for a fine-grained architecture is FPGA. FPGAs are commercially available reconfigurable devices and most of reconfigurable computing researches are done on them.

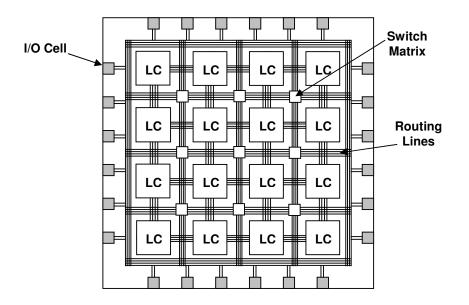

Fine-grained reconfigurable architectures are generally composed of configurable Logic Cells (LC), configurable Routing Sources, and Input-Output (I/O) Sources. The general structure of a fine-grained architecture is shown in Figure 2-2. The Logic Cells are connected to other ones using routing resources. There are switch matrices that determine how these cells and routing lines will be connected. I/O cells are also used to connect internal resources to the outside world.

Figure 2-2: General Structure of a Fine-Grained Architecture

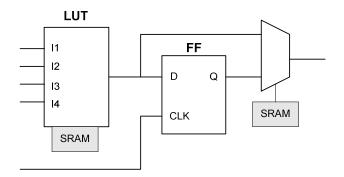

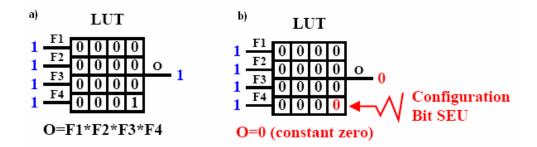

Logic Cells (or Logic Tiles) are used to implement logical functions. Most of the FPGA vendors use Lookup Table (LUT) to implement bit-level combinational logic functions on Logic Cells. For example, a LUT takes four input signals, gives one output signal on Virtex Family devices of Xilinx. The combinational function (4 inputs, 1 output) of LUT is encoded to 16 Bit and stored on configuration memory of FPGA. In addition to LUT, a Flip-flop (FF) is placed on same logic cell to generate synchronous circuits. Logic Cell structure of an SRAM based FPGA is shown in Figure 2-3

Figure 2-3: Basic Structure of a Fine-Grained Logic Cell on an FPGA

Fine-grained architectures can be used for a very broad range of applications since fine granularity allows mapping almost all types of applications. However, efficiency will decrease for some applications because of fine granularity. Therefore, only some applications can be classified as suitable for fine-grained architectures. The well-fitted applications such as image processing, data encryption need bit-level data handling [2]. In addition to these applications, finite state machines (FSMs) can be good candidates for mapping on fine-grained architecture (since state transitions of FSMs mostly depend on single bit values).

#### **Coarse Grained Architectures**

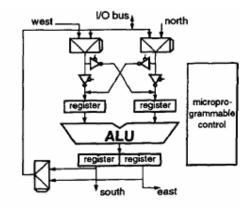

*Coarse Grained* architectures are composed of array of Processing Elements (PEs). Processing Elements are designed to compute word-level computations. They contain coarse grain structures such as an ALU or a small processor. Therefore, a datapath calculation can be easily mapped on coarse grain architectures. The word length of PE differs on different types of architectures. It ranges from 2 bit to 128 bit while most of them are 16 bit [3]. In Figure 2-4, the PE of KressArray is shown. It is called reconfigurable Datapath Unit (rDPU), and it has a 32-bit ALU and registers.

Figure 2-4: Reconfigurable Data Unit of KressArray [6]

The elements of the array are connected with a configurable routing. I/O ports connect the PEs to the outside world. The arrangement of the array differs according to the target application. Different array structures are available such as Mesh, Crossbar, Linear array, 2-Dimensional Array. In Figure 2-5, these structures are shown.

Linear arrays are designed as a pipeline with reconfigurable connections. Rapid and PipeRench are the popular linear array designs. *Mesh arrays* arrange PEs in two-dimension and they are connected with nearest neighbor. Popular mesh based course grained structures are MorphoSys, CHESS, Matrix, RAW and Garp. Some mesh structures add global connections to increase the performance of the array. These structures are also called *2-Dimensional arrays* and enables connection of arbitrary PEs. *Crossbar structures* connect all PEs with each other. However, this results in increased cost for the routing resources. PADDI-1 and PADDI-2 are the crossbar structures, which are intended to prototype datapath for Digital Signal Processing (DSP) Algorithms [4].

Figure 2-5: Array Structures of Coarse Grain Architectures a) Linear Array b) Mesh c) Crossbar d) 2-Dimensional Array

Some coarse grain architectures have also embedded routing structures and/or memory inside the PE. For example, KressArray-3 [5] has rDPU that contains an ALU and routing structure at the same time.

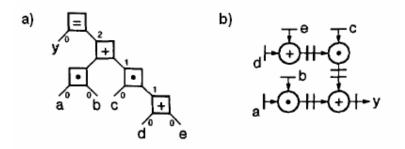

Datapath calculations can be easily mapped on coarse grain architectures. For instance, mapping of y = a \* b + c \* (d + e) on KressArray is shown in Figure 2-6.

Figure 2-6: A Datapath Equation and Hardware Mapping [6] a) Equation mapped to the node levels b) Hardware mapping of the equation

#### Fine vs. Coarse Granularity

Both structures have their own advantages and disadvantages. Finegrained architectures can implement any logic function in one clock cycle, which is impossible on coarse grain architectures. However, this flexibility is obtained by using high number of routing resources. The increase of routing sources results in some drawbacks. First, the area needed for routing will be much higher than logical elements in a fine-grained architecture. Power consumption increase and frequency decrease are other disadvantages of fine-grained structures. Routing sources of fine-grained architectures also need more configuration data than the coarse grain architectures. Because of higher configuration data, reconfiguration time of fine-grained architectures is higher than coarse-grained architectures.

Then why fine-grained FPGAs are extensively used instead of coarsegrained architectures? The reason may be flexibility dominates the other advantages of coarse-grained architectures. If an application can be mapped to coarse grain architecture, it can get high speed-up. However, another application cannot get considerable speedup, if it is not well suited on the same coarse grain architecture. This factor limits usage of one coarse grain architecture for different applications. Therefore, a unique coarse grain architecture is not available that can be used for all type of applications. Such a universal coarse grain structure does not seem to be available also in the future [5].

In addition, the compiler support of coarse grain architectures is still in its start stage. Current mapping tools cannot utilize the full potential of coarse-grained architectures due to the hardware complexity [7].

#### **Heterogeneous Architectures**

Heterogeneous architectures contain both fine and coarse grain elements to take advantage of both worlds. Usage of coarse grain elements results in an increase of the system performance. By using fine grain elements flexibility is maintained. Therefore, newer reconfigurable architectures are designed heterogeneously. Generally, arithmetic functions that occupy large space on fine grain blocks are moved to coarse grain blocks in heterogeneous architectures.

For example, Xilinx has embedded multiplier blocks into their FPGA devices starting from Virtex-II family. In newer devices, such as Virtex-4, there are multiply-accumulate (MAC) units, which are well fitted to Digital Signal Processing (DSP) filter implementations. These embedded units occupy less area, consume less power, and work with higher frequencies since they have a fixed routing inside. Therefore, embedded multipliers are much more efficient than implemented multipliers with fine grain elements.

### 2.3 RECONFIGURATION APPROACHES

#### **Dynamic (Run-Time) Reconfiguration**

If device is reconfigured according to the changing demands during the operation then it is called *dynamically reconfigurable* architecture. In such architectures, same hardware sources can be used for different purposes at different times by reconfiguring hardware. Therefore, the hardware becomes a *virtual hardware*, which looks like using infinite hardware resources on a system. In Figure 2-7, a dynamically reconfigurable system is shown.

Figure 2-7: Dynamic Reconfiguration of Hardware

Note that, *runtime reconfiguration* term is also used instead of dynamic reconfiguration.

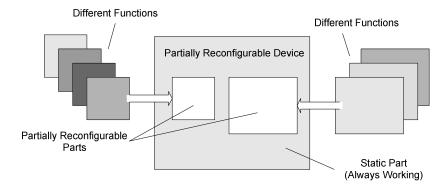

#### **Partial Reconfiguration**

*Partial reconfiguration* is a sub-class of runtime reconfiguration. According to the coming demands, only a part of these devices is reconfigured instead of reconfiguring whole device. In addition, while reconfiguring some parts of the device, remaining parts still operate in such partially reconfigurable devices. Therefore, different functions can be loaded to partially reconfigurable part while the other parts are working, as seen in Figure 2-8.

Figure 2-8: A Partially Reconfigurable Device and its Configurations

Partial reconfiguration has many benefits. For instance, the hardware on partially reconfigurable parts can be shared by different applications at different times. The other parts can be maintained as fixed parts that always remain active. The fixed parts can manage scheduling operations of reconfigurable parts. Therefore removing unnecessary hardware and inserting necessary ones to the system, results in reduced cost and power. In addition, system can operate without interrupting by keeping fixed part in contact with the outside world.

Partial reconfiguration property of reconfigurable devices is also used for speeding up the applications in some researches. For example, in [8] a CPU is placed on the fixed part and coprocessors are placed on reconfigurable parts of the FPGA. Different coprocessor configurations are prepared off-line and they are loaded to the reconfigurable parts with changing demands.

Another advantage of partial reconfiguration is reduced reconfiguration time. Since reconfiguration of full device is not needed, size of reconfiguration data also decreases. In other words, reconfiguration times are directly proportional with the reconfigured modules size. For example, if reconfiguration time of the entire device is 4 ms then quarter of the device can be reconfigured at 1 ms.

#### Self Reconfiguration

If the reconfigurable device reconfigures itself without any aid from the outside world then it is called *self-reconfigurable* system. Data required for different configurations are generally stored on standard storage mediums. A part of the device is responsible for taking data from the storage medium and sending this data to the configuration port of the device. The configuration of the device changes after port takes the data.

The main advantage of such reconfiguration is elimination of the need for external configuration controller. This results in reduction of the total system cost. Moreover, configuration data can be compressed at the storage side, and it can be decompressed by the configuration controller. Therefore, the size of the configuration data will decrease.

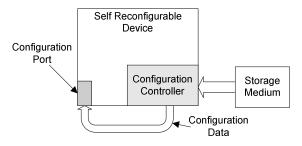

Different configuration port types can be used for self-reconfiguration. For example, if the device has only a configuration port available at external pins, then it can be used as shown in Figure 2-9. In this structure, configuration data is taken by configuration controller and it is sent to the external configuration port of the device. However, this approach has some drawbacks. Firstly, pins used by configuration controller cannot be used for different purposes. Secondly, the configuration data sent from configuration controller to configuration port cannot be secure since data signals must go through PCB.

Figure 2-9: Self-Reconfiguration from External Configuration Port

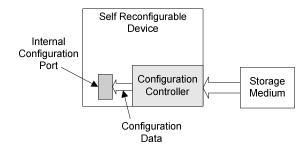

Some devices (such as Xilinx Virtex-II FPGA) have integrated configuration port inside the fabric of the device. The configuration controller can access this port internally (without going through pins) as shown in Figure 2-10. As a result, pins are not wasted for reconfiguration purpose and reconfiguration can be done securely.

Figure 2-10: Self-Reconfiguration using Internal Configuration Port

In some works such as [9] [10], this structure is used to implement a secure runtime reconfiguration. An initial configuration is loaded to the device that includes configuration controller and decryption hardware. The other parts are reserved for user applications and loaded by a partial reconfiguration. The partial configuration data is encrypted with a known key. This key is also stored on decryption circuit. Flow of secure partial reconfiguration occurs as follows: Encrypted configuration data is taken from an external source such as a storage medium or a radio link. Then it is decrypted by decryption circuit using the known key and passed to the configuration controller. Configuration controller writes

configuration data to the internal configuration port of the device and user application switches to another one. As a result, reconfiguration of user application becomes secure with this method since raw configuration data cannot be monitored from the outside world.

### 2.4 RECONFIGURATION TIME

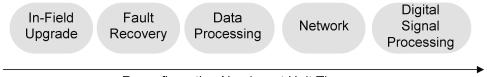

Reconfiguration time is an important criterion on runtime reconfigurable architectures. Especially the applications that use runtime reconfigurable architectures to speed up calculations need fast reconfiguration. The logic circuit inside reconfigurable part must be replaced with another logic circuit in a limited time for such applications. In Figure 2-11, distribution of different applications according to the reconfiguration frequency is shown. The overhead of this reconfiguration time must be compensated by speeding up the calculations by hardware.

Reconfiguration Number at Unit Time

#### Figure 2-11: Required Reconfiguration Times for Different Application Types

Reconfiguration time of commercially available FPGAs still takes around milliseconds. Therefore, the applications that take more than milliseconds at least can obtain a speedup by reconfiguring FPGAs. Generally, data processing applications are in this range. For example, encryption/decryption or sorting algorithms are good candidates to run on a runtime reconfigurable FPGA.

Some other devices such as DPGAs have been proposed to reduce the reconfiguration time to nanoseconds. However, they did not become commercially available due to their high costs (due to large configuration memory requirements) [11].

Nevertheless, the overhead of reconfiguration time can be reduced by dividing reconfigurable device into multiple parts and using scheduling algorithms.

Reducing reconfiguration time overhead allows mapping highly dynamic applications onto reconfigurable hardware [12]. Two types of scheduling algorithm can be used. These are runtime scheduling and design time scheduling.

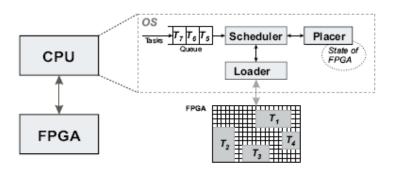

Scheduling of applications at runtime brings a new concept called *Hardware Operating System*. The hardware operating system work *online*, which means decisions are made during the system is running. Hardware operating systems also try to find solution for online placement of tasks onto different parts of the reconfigurable hardware. In Figure 2-12, elements of hardware operating system is shown.

Figure 2-12: An Example of Hardware Operating System [13]

Some works also try to reduce the reconfiguration delay by using offlinescheduling algorithms. For example, [14] assumes the sequence of the tasks is already known before running the system (i.e. at design time) and it reduces the reconfiguration overhead up to 40%.

## 2.5 PARTIALLY RUNTIME RECONFIGURABLE FPGAS

FPGAs are widely used devices on reconfigurable computing applications since most of them are inherently reconfigurable. A combination of a CPU and reconfigurable FPGA can be used as a reconfigurable platform. CPU can manage reconfiguration processes of the FPGA and map different hardware configurations to FPGA at different times. However, this structure is not so efficient since two devices are needed for this system. Instead, a *partially runtime reconfigurable* FPGA can do the tasks of both CPU and non-partially reconfigurable FPGA as a

System on Chip (SoC). FPGA can be divided into two parts in which one part is static and the other one is reconfigurable. Then a soft CPU can be mapped on the static part and it can manage reconfiguration processes of the reconfigurable part.

On a partially reconfigurable FPGA, more than one area can be reconfigured at an instance. Therefore, multiple tasks can be loaded at the same time and they can be reconfigured independent from the others .This is another advantage of using partial reconfiguration of FPGA.

Altera, Atmel, Lattice, QuickLogic, and Xilinx are the major FPGA vendors in the world. About half of them have FPGA products that offer partial runtime reconfiguration. These partially reconfigurable FPGA devices are listed below:

- Atmel AT6K

- Atmel AT40K

- Atmel AT94K

- Lattice ORCA

- Xilinx Virtex

- Xilinx Spartan

Xilinx Virtex and Spartan FPGA families can be partially reconfigured in a column-based approach. FPGA can be divided into columns and any of the columns can be reconfigured while the others are still running. There are also some restrictions to achieve partial reconfiguration. For example, the column boundaries must be determined at design time, the boundaries cannot change during execution. In addition, modules must communicate through special structures. Partial reconfiguration of Xilinx FPGAs will be discussed in further depth in Chapter 4.

Atmel AT6K, AT40K, and AT94K series FPGA can achieve runtime partial reconfiguration. The technology of reconfigurable logic inside FPGA is called *Cache Logic* by Atmel. The reconfigurable part can be any rectangle inside FPGA. AT94K series FPGA includes an AVR microcontroller embedded on FPGA. This microcontroller can change the logic inside the FPGA.

Lattice ORCA FPGA's can be partially reconfigured. For partial reconfiguration, the address is written with "Explicit" mode. Indeed every address frame is written into the bitstream, followed by the data frame for each address. Partial reconfiguration is done by setting a bitstream option in the previous

configuration sequence that tells the FPGA not to reset the entire RAM configuration during a reconfiguration [15].

### 2.5.1 Reconfiguration Times of FPGAs

Full reconfiguration time of Xilinx XCV50 is 1.2 ms with SelectMAP 8 bit parallel mode at 60 MHz with handshaking, where XCV50 is the smallest device of Virtex series FPGAs. Reconfiguration time for Atmel FPGA AT40K40 is 631 µs in parallel mode, with writing 16-bit wide words at 33 MHz [16]. Full reconfiguration of ORCA OR4E06 takes 5.94 ms [17]. Note that, these devices are smallest devices of the vendors. Newer and higher capacity FPGAs will have bigger configuration data. However, they also speed-up the configuration ports, which maintain reconfiguration times almost in the same order. For example, Xilinx Virtex-4 has a 32-bit SelectMAP configuration port, which can reach up to 100 MHz clock rates.

## 2.6 APPLICATION AREAS OF RECONFIGURABLE ARCHITECTURES

A wide range of applications can benefit from reconfigurable architectures. Some applications areas of the reconfigurable architectures are listed below.

- Easy Prototyping, Low Volume Products

- Field Upgrade of Hardware

## 2.6.1 Easy Prototyping – Low Volume Products

A digital Application Specific Integrated Circuit (ASIC) can be prototyped using a reconfigurable architecture. To accomplish this, different hardware configurations are mapped on a reconfigurable architecture at design time. After verifying correct operation of the designed circuit, an ASIC can be produced. If this circuit is not a mass product, reconfigurable device can also be used as a final product. Hence using a reconfigurable device will eliminate costly processes of producing an ASIC device.

### 2.6.2 In-Field Upgrades

Being a reconfigurable architecture also provides some other unique properties. Reconfigurable devices provide an opportunity to change hardware on the fly. In other words, the device can be reconfigured easily by writing configuration data to the configuration memory. This feature can be used on systems that need upgrade of hardware structure during operation. In such systems, reconfigurable device can be used as a heart of the system. A remote computer can connect to the system and send configuration data. Then hardware structure can be changed by reconfiguring the device with the new configuration data. Since hardware components are generally base of a system, reconfiguration can almost replace whole architecture with a new one. This type of upgrade can save time and money for the producer.

Even there may be conditions such that it may be impossible to upgrade device without in-field upgrade. For example, servicing or replacing components physically is impossible on a satellite system. In such architectures, using reconfigurable architecture that can be reconfigured with a remote connection is inevitable. As a result, reconfigurable devices are ideal components for systems that need in-field upgrade operations. Some works [10] deal with partial reconfiguration of hardware that eases in-field upgrades.

## 2.7 APPLICATION AREAS OF RUNTIME RECONFIGURABLE ARCHITECTURES

Changing the hardware on a running system is possible by using Runtime Reconfigurable architecture. This feature enables using runtime reconfigurable architecture as a *virtual hardware* source. In other words, different hardware configurations can be used at different times by RTR. Many applications can benefit from this feature to save cost, power, and resource usage on digital circuits. Moreover, applications can get speedup by using RTR, since it provides a flexible dedicated hardware for different functions. As a result, RTR can be used for the following purposes:

- Cost and power reduction

- Designing an Adaptable Computing Platform

- Designing Fault Tolerant Circuits

- Speeding-up Computations

### 2.7.1 Cost and Power Reduction

RTR can reduce needed resource size if the required hardware can be divided into multiple parts. These smaller parts can be mapped to the hardware by generating configurations. Then these configurations can be loaded to the device at different times by using RTR. A scheduler arranges the reconfiguration operations according to the demands. Therefore, a smaller capacity device can be enough to map a bigger circuit on it. This results in cost and power reduction of the system.

For example, Lianos et al. proposed a space efficient method for calculating Fast Fourier Transform (FFT) by using a dynamically reconfigurable architecture [18]. One reconfigurable vector calculates a column of FFT then feeds the outputs into the reconfigurable vector again to calculate consecutive stages of the FFT. Therefore, only one reconfigurable vector is enough to calculate FFT on a dedicated hardware by using RTR.

In another work [19], a reconfigurable architecture is implemented that behave as Programmable Logical Controller (PLC). Designed architecture utilizes Temporal Petri Net language to describe applications. The sequential structure of Petri Nets allows splitting applications into multiple parts. Then these parts are mapped to same FPGA and used sequentially by reconfiguring it. This architecture can divide whole application up to 40 parts. Therefore, using 40 times smaller capacity FPGA can be enough instead of using a big one. This can reduce the cost of device from \$317 to \$38.

Widespread usage of mobile systems increased the demand for low power consumption while maintaining high performance. Some works deals with mobile systems that use dynamic reconfiguration to reduce the total power of the system. In [20], control units of an automobile are implemented on a runtime reconfigurable FPGA. The user area is divided into four smaller parts. High number of control units (e.g. 20 units) that cannot fit to one-device shares available sources by time multiplexing. A scheduler determines reconfiguration

processes of control units. As a result, the system only consumes power of four control units for implementing much higher number of control units. In addition, a part of FPGA is always kept in contact with the outside world since only necessary parts reconfigured. This eliminates a need for external controller of reconfiguration process, which contributes power and cost reduction.

### 2.7.2 Adaptable Computing

Some types of applications require adaptation of hardware to changing demands. In such applications, implementing circuits on a static device is impossible, even a highest capacity one is used. The ultimate solution of this problem is using a reconfigurable hardware. Infinite number of configurations can be prepared and reconfigurable hardware can be reconfigured with new demands.

Furthermore, many applications can benefit from reusability of hardware on reconfigurable architectures. Computations can be divided into multiple parts and they can be computed one after another with a parallel processing structure. If the gain obtained on area usage compensates the latency, the reconfigurable architecture can be preferred. For example, a matrix multiplication method proposed by L. Jianwen et al. [21] can do matrix multiplication with 80% less area than linear array structure. It have also used approximately 50% less area than linear array structure in terms of AT Metric (product of area and latency)

Some of the adaptable-computing applications absolutely need reconfigurable architectures are the following:

### **Evolvable Hardware**

Evolvable Hardware is the application of Genetic Algorithms on circuits. Evolvable algorithms can find a circuit from its behavioural description [22]. There are two methods available to achieve this goal. One of them, known as Extrinsic Evolvable Hardware, simulates alternative circuit configurations and selects the best one. The other method, known as Intrinsic Evolvable Hardware, directly tests alternative circuit configurations on hardware. Then best of the configuration is selected [23]. It is necessary to use a reconfigurable hardware to test large number of alternative configurations. Therefore, RTR is necessary to implement Evolvable Hardware with the second method. Hardware implementations of Robotics or Artificial Neural Networks also require such evolvable structures. Therefore, they are the candidates of RTR applications.

### Software Defined Radio

Software Defined Radio (SDR) is another concept that involves adaptable hardware sources inside. SDR is a wireless platform that can work with different communication protocols. It can adapt to a communication protocol just by downloading and changing the configuration on the platform as a software module. SDR requires a large amount of digital signal processing operations. For this reason, SDR systems generally use a Digital Signal Processor (DSP) and an FPGA as a coprocessor [24]. DSP makes software operations whereas FPGA implements different filters and reconfigured with changing necessities. However, it is possible to use only one runtime reconfigurable FPGA to do operations of both DSP and FPGA. This runtime reconfigurable FPGA can be divided into two parts where one part is static and the other one is dynamic. Static part can be loaded by a soft processor core. Dynamical part can be reconfigured to run alternative coprocessor cores. Some researches (such as [25] and [26]) deal with such single chip systems that can reconfigure themselves with changing demands.

### 2.7.3 Speeding-up Computations

Reconfigurable Architectures (RAs) provide a flexible structure as microprocessors. Microprocessors allow changing the software and RAs allow changing hardware. Dedicated hardware on RA enables parallel computing while software on microprocessor allows only serial operations. Therefore, implementing a computational task on a dedicated hardware on RA is much faster than executing on a processor as software.

Reconfigurable architectures can be used to accelerate computational tasks by mapping algorithms or parts of them to the dedicated hardware. For each different computational task, hardware can be reconfigured to map calculations on hardware. The rate of computations changes also affects the reconfiguration period of the hardware. If reconfiguration overhead is less than the gain obtained by mapping calculations on hardware, a considerable speed-up can be achieved.

Moreover, it is known that more than 90% of time is consumed on 10% of code in most of the software programs [27]. These codes are generally nested loop statements, which intend to take longer time than other structures. If the statements inside a loop can be mapped directly on hardware, execution time will decrease. The hardware on the reconfigurable architectures can be used for such loop statements. For each loop statement, an alternative configuration is created. Then by using runtime reconfiguration, infinite number of loop statements can be mapped on hardware. Therefore, the software can be executed more parallel, and it can be accelerated more.

Many algorithms such as image processing, image compression /decompression, data encryption/decryption may benefit from the parallelism of reconfigurable architectures. The only necessity to get a speedup is reconfiguration time cost must be lower than the gain obtained with parallelism.

### 2.7.4 Fault Tolerant Systems

Fault tolerance on hardware generally requires reserving spare sources and replacing faulty sources with spare ones. Reserving spare sources is a trivial issue on reconfigurable devices since they are composed of array of identical elements. Many researches such as [28], [29] and [30] use inherent reconfiguration property of the FPGAs in order to tolerate faults on them. In Chapter 5, researches dealing with this topic will be discussed in more detail.

### 2.8 APPLICATION IN THIS WORK

A fault tolerant hardware was also designed in this work, which uses RTR property of an FPGA. Faults were eliminated using reconfiguration of the hardware. Furthermore, fault injection was done with the help of RTR. In Chapter 5, working principle of designed architecture will be explained in more detail.

# **CHAPTER III**

# **XILINX FPGA ARCHITECTURE AND TOOLS**

In this chapter, the general architecture of Xilinx FPGAs will be explained. At necessary points, examples will be given from Virtex-E or Spartan-2E series of FPGAs.

## 3.1 MAIN STRUCTURE OF XILINX FPGAS

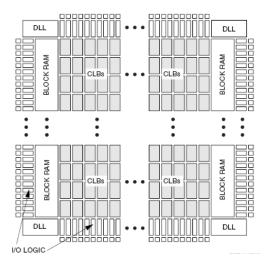

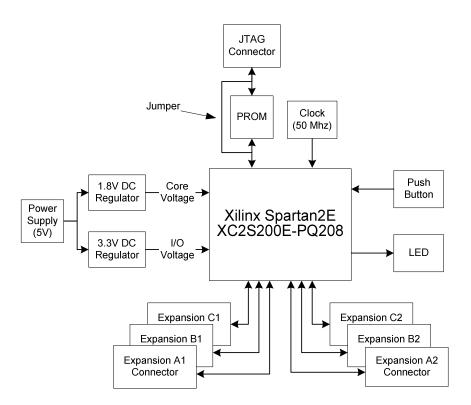

Xilinx FPGA's are composed of Configurable Logic Blocks (CLB), Input Output Blocks (IOB), BlockRAM's (internal RAM), and the configurable routing matrix. Array of CLBs forms the FPGA structure. They are connected using routing lines and they implement logic functions. For example, the device used in this work, XC2S200E has 28 rows and 42 columns of CLBs. The structure of Spartan 2E FPGA is shown in Figure 3-1.

Figure 3-1: General Structure of Spartan 2E FPGAs [31]

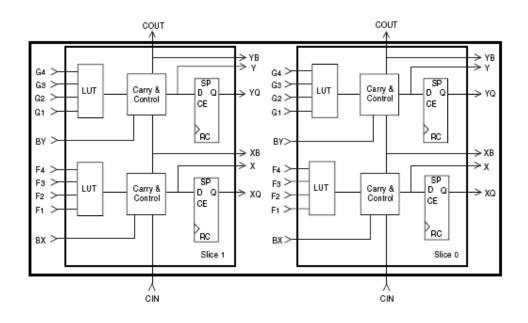

### 3.1.1 Configurable Logic Block Structure

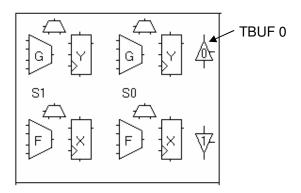

Each Configurable Logic Block (CLB) has two identical slices each of which have two Logic Cells (LCs). These logic cells are the basic building block of the FPGA. There is one flip-flop as storage elements and one look-up table which implements combinational logic in a LC. Also, carry logic elements are inserted to speed-up arithmetic operations. A CLB structure of Virtex-E or Spartan 2E device is shown in Figure 3-2. Note that CLB architectures of Virtex-E and Spartan 2E are same.

Figure 3-2: A CLB of a Virtex-E (or Spartan 2E) device

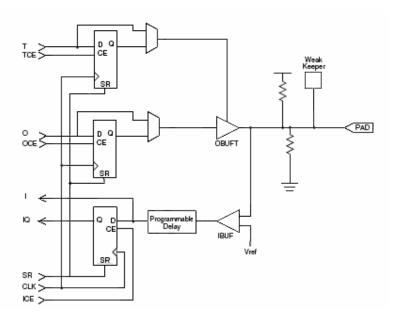

### 3.1.2 Input Output Block Structure

FPGAs are connected to the outside world using programmable Input Output Blocks (IOBs). As shown in Figure 3-3, an IOB include flip-flops (FF) for input, output and tri-state enable signal. These FFs can be used to obtain minimum FF to pin delay. In addition, a number of IOBs are grouped to form a bank. Voltage levels of banks can be selected from different types of I/O standards.

Figure 3-3: Input/Output Block Structure of Virtex-E Device

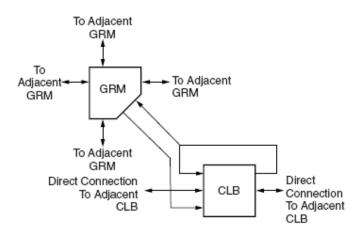

# 3.1.3 Routing Structure

Routing structure is reconfigurable on Xilinx FPGAs, which is one of the necessities to be a reconfigurable device. It is also adjusted in a hierarchical manner to make it area efficient. There are mainly four types of routing resources:

- Local Routings are used to make connections inside the CLB, between CLB and General Routing Matrix (GRM), and between two CLBs.

- General Purpose Routing connects most of the signals on the FPGA. CLB's are connected to other resources using GRM switch. In addition, a GRM is connected to adjacent six GRMs. GRM connections are shown on Figure 3-4. These switches also connect horizontal and vertical lines. These vertical and horizontal long lines span the full height/width of the FPGA.

Figure 3-4: General Routing Matrix and its Connections [31]

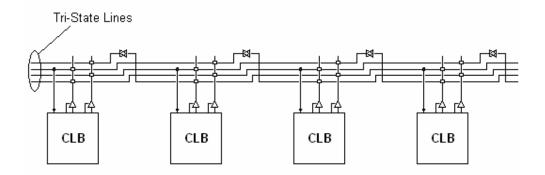

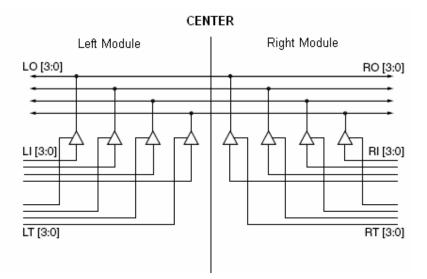

Dedicated Routing sources connect special signals on the FPGA. For example, there are four signal lines horizontally placed on the FPGA for each CLB row as shown in Figure 3-5. These lines can be used for tristate bus implementation. In this work, tri-state lines were used to implement a bus inside the FPGA. This bus is called bus-macro and will be described in detail in Chapter 4.

Figure 3-5: Horizontal Longlines that traverse all along the FPGA

• *Global Routings* are used for low skew and high fanout signals such as clock signals

### 3.2 CONFIGURATION ARCHITECTURE OF XILINX FPGAS

Xilinx FPGAs have SRAM based configuration memory, which provides unlimited reprogramming feature. The configuration file of a Xilinx device is called *bitstream*. A host device sends this bitstream file to one of the configuration ports of the FPGA. Then internal state machines of the FPGA device evaluate if the bitstream file has correct Cyclic Redundancy Check (CRC) value or not. If the CRC value is correct then it programs the configuration memory (SRAM) of the device with the bitstream data.

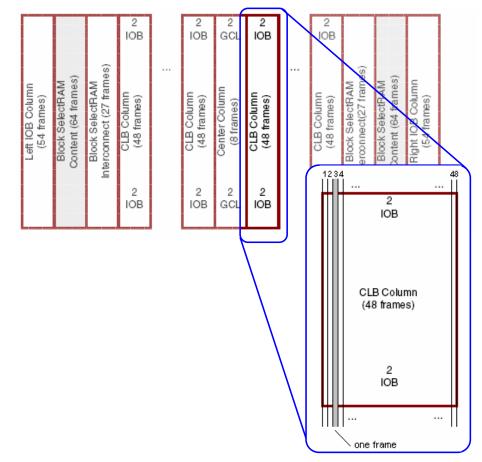

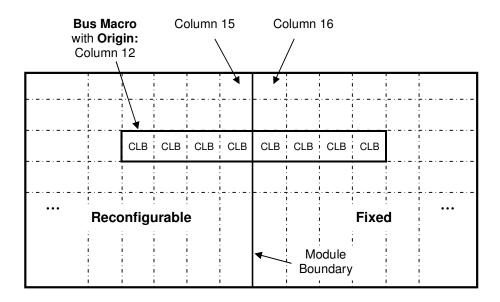

The configuration data of FPGA has divided into frames. A *frame* is the minimum segment of configuration memory that can be reconfigured. A frame includes configuration information of full height of device with one bit wide. Since a frame includes the configuration data of full height of the device, minimum reconfigurable unit must occupy full height of the device.

Since configuration bitstream is divided into frames in a column-based order, at least a column of CLBs can be reconfigured at the same time. Moreover, configuration information of one CLB column is stored on 48 frames on XCV50 device [32]. Therefore, reconfiguration of 48 frames is necessary to reconfigure a column of CLBs. The configuration memory structure of XCV50 device is shown in Figure 3-6.

Figure 3-6: Configuration Columns and Frames of Xilinx XCV50 device

# 3.2.1 Column and Difference Based Reconfiguration

Xilinx FPGAs allows two types of partial reconfigurations; column and difference based reconfigurations. It is possible to reconfigure one or more columns of CLBs using column based reconfiguration flow. On the other hand, difference based reconfiguration allows small changes on the configuration data.

If boundary between two CLB column are defined strictly (i.e. no routing connection between) then reconfiguration of one column does not affect the other. By using this principle, *modules* that occupy integer multiple of CLB columns can be partially reconfigured. This type of reconfiguration is called column-based reconfiguration.

Another possibility for reconfiguration is making small changes on the configuration memory. Internal configurations of a CLB can be changed by reconfiguring them. For example, the function of Lookup Table inside a CLB may be changed from an OR gate to a AND gate. The bitstream generation tools will compare two different bitstreams and generate a bitstream that includes only different frames. The resulting bitstream will be much smaller than the original ones.

### 3.2.2 Glitchless Reconfiguration

"FPGA memory cells have glitchless transitions, when rewritten, the unmodified logic will continue to operate unaffected" [33]. This glitchless reconfiguration is required for communication channels that pass through from a reconfigurable module. Otherwise, reconfiguration of the module will break the communication channel and connection will be lost.

Glitchless reconfiguration property is supported on Spartan 2, Spartan 2E, Virtex, Virtex E, Virtex 2, Virtex 2 Pro, and Virtex 4 devices of Xilinx. Spartan 3 and Spartan 3E devices do not reconfigure without glitches [34].

### 3.2.3 Clocking Logic

Same clock can route to all partial modules. However, clocking logic (Clock Routing Paths, Clock IOB) is always separate from the reconfigurable module and clocks have separate bitstream frames [35]. As a result, reconfiguration of a module does not affect synchronous circuits on another module.

# 3.2.4 Suitable Configuration Options for Runtime Reconfiguration

Xilinx FPGA devices can be configured using different configuration interfaces [36]. These interfaces are

- Master / Slave Serial Mode,

- SelectMAP Interface,

- Boundary Scan (JTAG) port and

• Internal Configuration Access Port (ICAP).

Master Serial Mode is used to configure FPGA from a PROM device. SelectMAP is a parallel bus available at normal I/O pins of the FPGA. Boundary scan port is a standard test port that has dedicated pins on FPGA. ICAP is an internal port that is similar to the SelectMAP interface.

One of these configuration interfaces is selected at power-up according to the configuration mode pins, M0, M1, and M2. Because data pins of the configuration interface must be reserved to one of the interfaces at start-up. However, it is not necessary to make mode selection for boundary scan mode since it is always available for configuration independent of the mode selection [31]. ICAP also does not need any mode selection since it is an internal interface.

To make a runtime reconfigurable system using a Xilinx FPGA, a suitable configuration scheme must be constructed. FPGA must be configured initially and it must be reconfigured while initial configuration is operating on it. It is possible to use different configuration interfaces for these initial and run-time reconfigurations. However, not all of these methods are suitable for run-time reconfiguration. The methods suitable for run-time reconfiguration are

- SelectMAP Interface,

- Boundary Scan (JTAG) port and

- Internal Configuration Access Port (ICAP).

Note that, one of these modes is necessary for only runtime reconfiguration. Loading initial bitstream can be done by any method. For example, the initial bitstream can be loaded using a serial PROM then all reconfigurations can be done using ICAP port. As another example, loading initial bitstream and reconfiguration can be done using JTAG port.

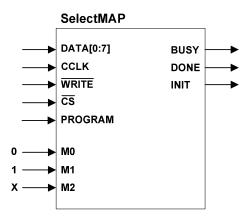

### Slave Parallel Mode (SelectMAP)

SelectMAP is a parallel bus, which is driven by an external device to program the FPGA. In normal operation, SelectMAP pins are left to the user after configuration as normal I/O pins. However, in a runtime reconfigurable system they must be always available as a SelectMAP interface to enable runtime reconfiguration. In order to achieve this, when creating bitstream with Xilinx BitGen tool, *-g Persist:Yes* option must be used. This option ensures that the SelectMAP interface will remain active after first configuration.

Essential signals used for SelectMAP configuration port are given in Figure 3-7. Configuration data is sent or received through DATA pins synchronized with CCLK Clock. BUSY is used for handshaking and not necessary for low clock rates. CS is the Chip Select signal that enables the port for data transfers. WRITE is used to select the operation type, either as write or as read. PROG, INIT, and DONE signals are the SelectMAP protocol commands and acknowledgements such as "reset the configuration logic", "verify successful operation" etc... More details about the SelectMAP protocol can be found on [37].

Figure 3-7: SelectMAP Configuration Signals on Xilinx FPGA

The main advantage of the SelectMAP interface is fast configuration opportunity it provides. It is possible to use a SelectMAP up to 50 MHz clock rates without handshaking (Virtex, Virtex-E, and Spartan-2). For Virtex-2, this frequency is 66 MHz [37]. Therefore, SelectMAP can provide bandwidths of higher than 500 Mbit/sec, since it is 8-bit parallel bus.

SelectMAP has also some shortcomings. It requires either an external controller or some parts of FPGA to control the bus. An external controller is an extra cost. When controller logic is implemented on the same FPGA, it limits the reconfigurable areas since controller must access to external pins. Furthermore, it occupies logic and BlockRAM sources, which can be necessary for the user.

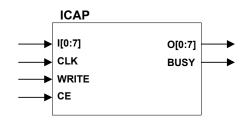

#### Internal Configuration Access Port (ICAP)

Internal Configuration Access Port (ICAP) enables configuring FPGA from logic inside the fabric. It has same protocol with the SelectMAP configuration port. The only difference is the connection points, which are the internal routings on ICAP instead of I/O pins. Therefore, a logic mapped inside the device can reconfigure FPGA by writing configuration data to the ICAP. However, hardware communicating with ICAP port must not be reconfigured since communication can be lost after reconfiguration. Therefore, it is more suitable for partial reconfiguration instead of full reconfiguration [56].

ICAP is a very good solution for self-reconfiguration since it does not require any external hardware sources. It can take advantages of selfreconfiguration such as secure configuration and compressed bitstreams. Unfortunately, it is only available on newer Xilinx devices such as Virtex-II and Virtex-4 FPGAs.

Figure 3-8: ICAP Configuration Signals on Xilinx FPGA

ICAP interface signals are shown in Figure 3-8. The functionalities of CLK, WRITE and BUSY signals are equivalent on ICAP and SelectMAP. In addition, CE has the same function with CS on SelectMAP. The only difference is the data bus, which is divided into two parts on ICAP. One part (I[0:7]) is used for writing configuration data to port, while the other part (O[0:7]) is used for reading back the configuration data.

#### Boundary Scan (JTAG) Mode

Joint Test Action Group (JTAG) designed a test standard and named JTAG for testing Printed Circuit Boards (PCB). This Boundary Scan architecture is

designed to test the physical connection of I/O pins at the board level. JTAG become a widely used test port with the increase of complicated PCB structures and smaller Integrated Circuits (ICs) [38]. Due to lots of benefits, it has become an IEEE standard (IEEE 1149.1). Most of current ICs contain a JTAG port pins to debug it. Its boundary scan architecture has a four-wire serial interface travels along all the pins of the device forming a chain. Serial data enters to the device with Test Data In (TDI) pin and stored on a shift (instruction) register. The data is send to the output of the device with Test Data Out (TDO) pin. All data shifting on JTAG chain are done with synchronized to Test Clock (TCK). The reserved pins for the JTAG port and their acronyms are listed in Table 3-1.

| Pin Name | Description      |

|----------|------------------|

| TDI      | Test Data In     |

| TDO      | Test Data Out    |

| TMS      | Test Mode Select |

| ТСК      | Test Clock       |

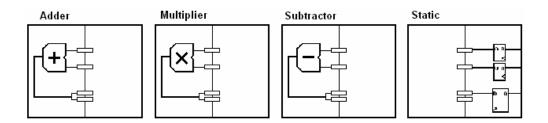

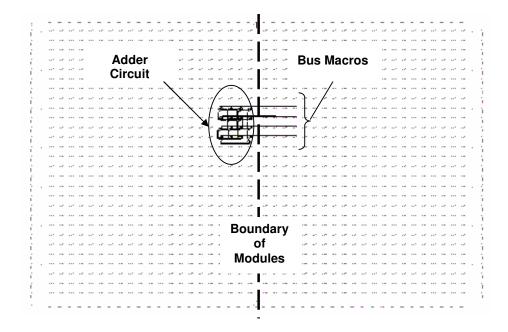

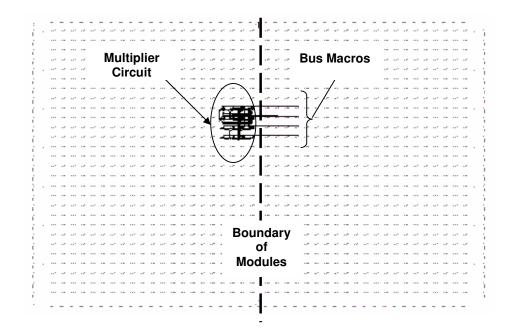

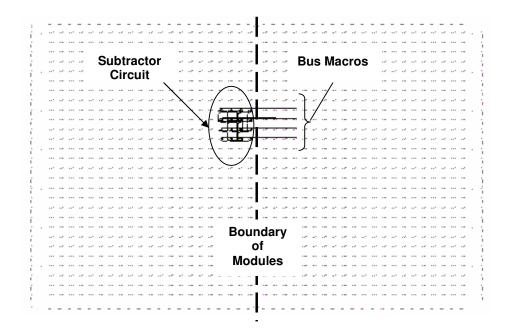

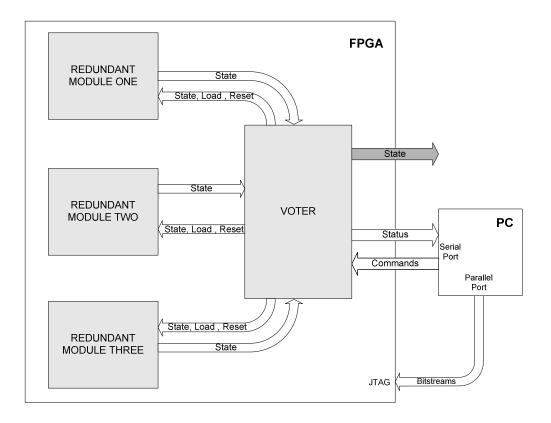

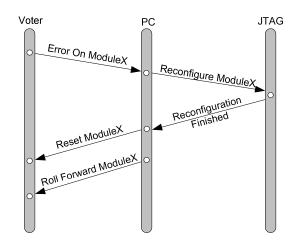

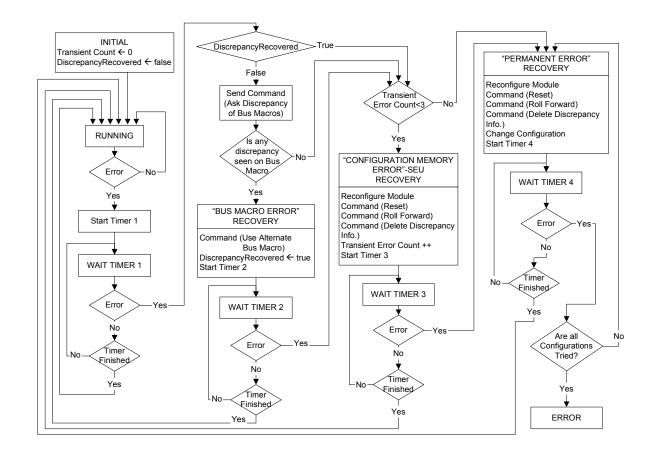

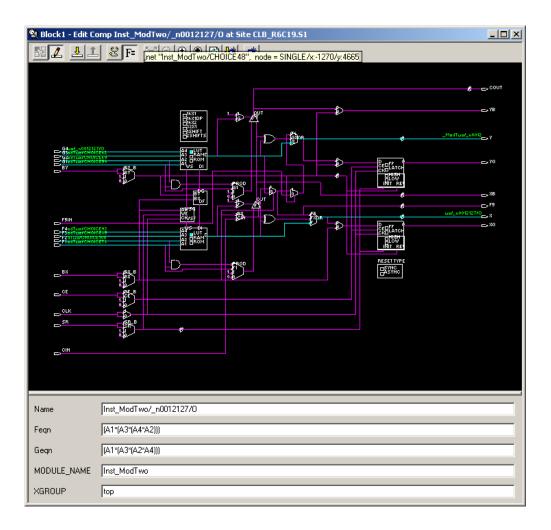

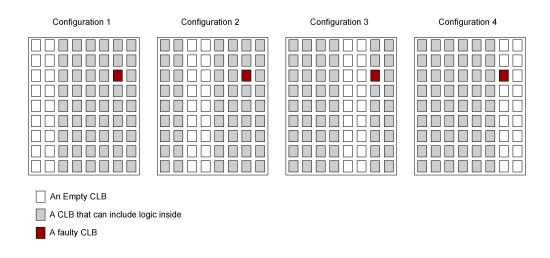

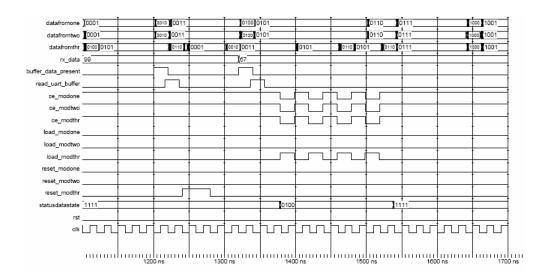

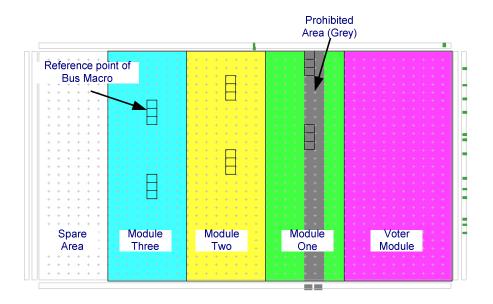

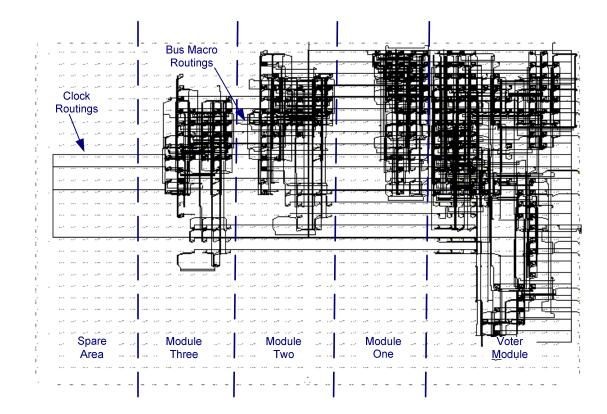

Table 3-1: JTAG Pins and their descriptions